# TRACE-BASED LEARNING FOR AGILE HARDWARE DESIGN AND DESIGN AUTOMATION

A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by Yuan Zhou May 2021 © 2021 Yuan Zhou ALL RIGHTS RESERVED

# TRACE-BASED LEARNING FOR AGILE HARDWARE DESIGN AND DESIGN AUTOMATION

### Yuan Zhou

Cornell University, May 2021

Modern computational platforms are becoming increasingly complex to meet the stringent constraints on performance and power. With the larger design spaces and new design trade-offs brought by the complexity of modern hardware platforms, the productivity of designing high-performance hardware is facing significant challenges. The recent advances in machine learning provide us with powerful tools for modeling and design automation, but current machine learning models require a large amount of training data. In the digital design flow, simulation traces are a rich source of information that contains a lot of details about the design such as state transitions and signal values. The analysis of traces is usually manual, but it is difficult for humans to effectively learn from traces that are often millions of cycles long. With state-of-the-art machine learning techniques, we have a great opportunity to collect information from the abundant simulation traces that are generated during evaluation and verification, build accurate estimation models, and assist hardware designers by automating some of the critical design optimization steps.

In this dissertation, we propose three trace-based learning techniques for digital design and design automation. These techniques automatically learn from simulation traces and provide assistance to designers at early stages of the design flow. We first introduce **PRIMAL**, a machine-learning-based power estimation technique that enables fast, accurate, and fine-grained power modeling

of IP cores at both register-transfer level and cycle-level. Compared with gatelevel power analysis, PRIMAL achieves an average error within 5% while offering an average speedup of over 50x. Secondly, we present **Circuit Distillation**, a machine-learning-based methodology that automatically derives combinational logic modules from cycle-level simulation for applications with stringent constraints on latency and area. In our case study on network-on-chip packet arbitration, the learned arbitration logic is able to achieve performance close to an oracle policy under the training traffic, improving the average packet latency by 64x over the baselines while only consuming area comparable to three eight-bit adders. Finally, we discuss **TraceBanking**, a graph-based learning algorithm that leverages functional-level simulation traces to search for efficient memory partitioning solutions for software-programmable FPGAs. TraceBanking is used to partition an image buffer of a face detection accelerator, and the generated banking solution significantly improves the resource utilization and frequency of the accelerator.

### **BIOGRAPHICAL SKETCH**

Yuan Zhou received his bachelor's degree in Electronics Engineering from Tsinghua University, Beijing, China in 2015. He then joined the School of Electrical and Computer Engineering (ECE) at Cornell University as a Ph.D. student. Since then, Yuan studied under the supervision of Prof. Zhiru Zhang at the Computer Systems Laboratory, where he passed his Ph.D. candidacy exam and received a Master of Science degree in ECE in March 2019. During his graduate study, Yuan has worked on a variety of research areas, including high-level synthesis, deep learning acceleration, benchmarking, and application of machine learning in digital design. He interned at NVIDIA research and Google in summer 2018 and summer 2020, respectively. For everyone who has faith in me.

### ACKNOWLEDGEMENTS

I sincerely appreciate the support from my family, my friends, my mentors, and all other people who have helped and encouraged me during my graduate study. This dissertation would not have been possible without their support.

First and foremost, I would like to thank my advisor, Prof. Zhiru Zhang, for his support and supervision during my Ph.D. Zhiru saw my potential of becoming a researcher and brought me into CSL. In the past five-and-a-half years, Zhiru advised me patiently and consistently provided precious suggestions to my research. Zhiru always encouraged me and had faith in me, even when I was questioning myself.

I would also like to thank my dissertation committee members: Prof. David Albonesi, Prof. Adrian Sampson, and Dr. Mark Haoxing Ren. I thank Dave for detailed suggestions on my dissertation and concrete feedback on my power estimation work from a circuit expert's perspective. His comments during our discussions made me realize the value of high-level modeling and pointed me in the direction of research that is actually important to hardware designers. I thank Adrian for being a very supportive mentor and an inspiring source of research ideas. Adrian also taught me a lot about programming languages and compilers, which will be very useful for the first job in my career. Last but not least, I would like to thank Mark for being my mentor during my internship at NVIDIA in 2018 and serving on my committee afterwards. It was from a discussion with Mark and other collaborators where we got the idea of accelerating power estimation with machine learning. Mark pointed me to the correct direction during my internship and continued to provide suggestions to my research after I left NVIDIA.

I am grateful to all members of the Zhang research group and the CSL com-

munity for building such a lively and friendly environment for my research and daily life. Specifically, I really appreciate the help from the Zhang group alumni: Dr. Steve Haihang Dai, Dr. Gai Liu, Dr. Ritchie Zhao, Dr. Nitish Srivastava, Dr. Zhenghong Jiang, and Prof. Cunxi Yu. They got me familiar with the research infrastructure in our group, provided valuable suggestions on how to be successful during my Ph.D., and served as a great source of research ideas. I acknowledge all the hard work from my collaborators within and outside of Cornell, and I thank Weizhe Hua, Yu Gan, and Chenhui Deng for inspiring research discussions. I would also like to thank my friends at CSL and all members of the Zhang group for the fun activities, including badminton, table tennis, card games, and picnic. Special thanks to Bo Yuan at Google and Dr. Yanqing Zhang at NVIDIA for being outstanding mentors during my internships and providing valuable suggestions to my future career.

Finally, I would like to express my deepest gratitude to my parents, Fugen Zhou and Wenyan Liu, for raising me to become who I am today and always being supportive throughout my graduate study. Also, I would like to deeply thank my girlfriend Mengyao Xu, for being loving, caring, and supportive in the past three years.

|   | Ded<br>Ack<br>Tabl<br>List                | graphical Sketch                                                                                                                   | iii<br>iv<br>v<br>vii<br>ix<br>x |

|---|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1 | <b>Intr</b><br>1.1                        | oduction<br>Challenges in Digital Design: Productivity and Quality                                                                 | 1<br>3                           |

|   | 1.1                                       | Trace-Based Design-Specific Learning for Agile Hardware Design                                                                     | 5                                |

|   | 1.2                                       | Dissertation Overview                                                                                                              | 7                                |

|   | 1.4                                       | Collaborations, Funding, and Previous Publications                                                                                 | 10                               |

| 2 | Preliminaries on EDA and Machine Learning |                                                                                                                                    |                                  |

|   | 2.1                                       | Overview of the EDA Flow                                                                                                           | 13                               |

|   | 2.2                                       | Machine Learning Overview                                                                                                          | 18                               |

|   |                                           | 2.2.1 Linear and Tree-Based Models                                                                                                 | 20                               |

|   |                                           | 2.2.2 Deep Learning                                                                                                                | 23                               |

|   |                                           | 2.2.3 Reinforcement Learning                                                                                                       | 27                               |

| 3 |                                           | MAL: Power Inference Using Machine Learning                                                                                        | 31                               |

|   | 3.1                                       | Methodology                                                                                                                        | 34                               |

|   |                                           | 3.1.1 RTL Power Estimation Methodology                                                                                             | 36                               |

|   | 2.2                                       | 3.1.2 HLS Power Estimation Methodology                                                                                             | 37                               |

|   | 3.2                                       | Feature Construction                                                                                                               | 40<br>40                         |

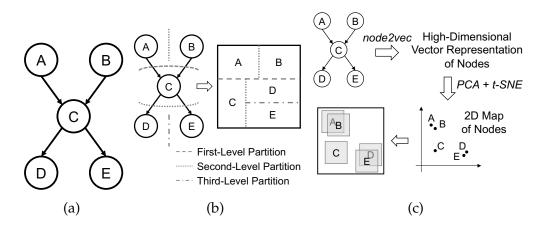

|   |                                           | <ul><li>3.2.1 Feature Encoding for Cycle-by-Cycle Power Estimation</li><li>3.2.2 Mapping Registers and Signals to Pixels</li></ul> | 40<br>42                         |

|   |                                           | 3.2.3 Feature Construction for HLS Power Estimation                                                                                | 44                               |

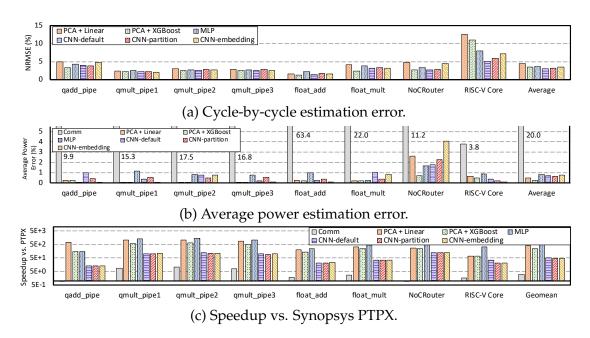

|   | 3.3                                       | Experimental Results for RTL Power Estimation                                                                                      | 45                               |

|   | 0.0                                       | 3.3.1 Benchmarks                                                                                                                   | 45                               |

|   |                                           | 3.3.2 Results                                                                                                                      | 46                               |

|   | 3.4                                       | Experimental Results for HLS Power Estimation                                                                                      | 51                               |

|   | 3.5                                       | Related Work and Discussions                                                                                                       | 55                               |

| 4 |                                           | uit Distillation: Distilling Arbitration Logic from Traces using Ma-                                                               | ,                                |

|   |                                           | ne Learning                                                                                                                        | 58                               |

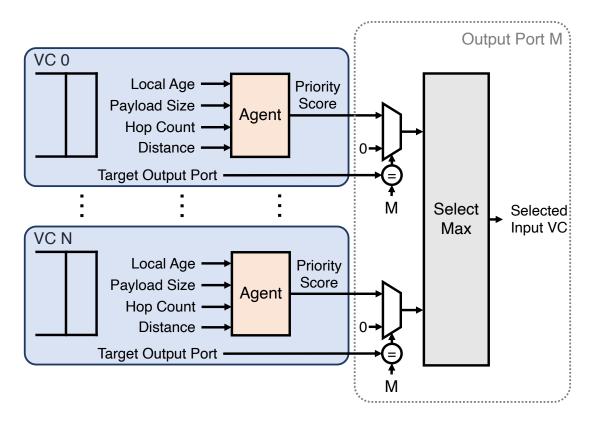

|   | 4.1                                       | NoC Arbitration Background                                                                                                         | 61                               |

|   | 4.2                                       | Distilling Arbitration Logic from Data                                                                                             | 62                               |

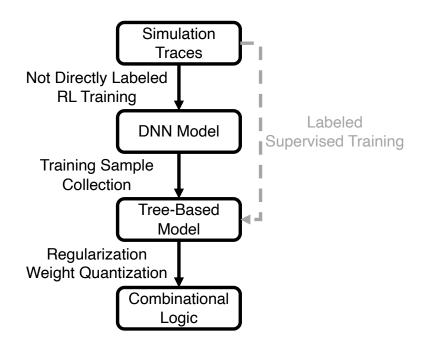

|   |                                           | 4.2.1 Step 1: Learning an Arbitration Policy                                                                                       | 63                               |

|   |                                           | 4.2.2 Step 2: Selecting the Tree Model                                                                                             | 65<br>65                         |

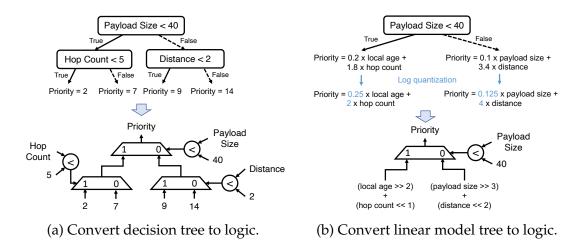

|   | 12                                        | 4.2.3 Step 3: Generating Implementable Logic                                                                                       | 65<br>67                         |

|   | 4.3                                       | Case Study: NoC Arbitration Policy                                                                                                 | 67                               |

# TABLE OF CONTENTS

|    |       | 4.3.1 Area and Performance of the Distilled Arbitration Logic . | 70  |

|----|-------|-----------------------------------------------------------------|-----|

|    |       | 4.3.2 Analysis of the Distilled Arbitration Logic               | 71  |

|    |       | 4.3.3 Generalization to Different Injection Rates               | 72  |

|    |       | ,                                                               | 74  |

|    | 4.4   | Related Work and Discussions                                    | 75  |

| 5  | Trac  | e-Based On-Chip Memory Banking for Software-Programmable        |     |

|    | FPG   | GAs                                                             | 79  |

|    | 5.1   | Motivational Example                                            | 81  |

|    | 5.2   | -                                                               | 84  |

|    |       |                                                                 | 86  |

|    |       |                                                                 | 88  |

|    |       |                                                                 | 89  |

|    | 5.3   | SMT-Based Verification                                          | 92  |

|    | 5.4   | Experimental Results                                            | 94  |

|    |       | 5.4.1 Results on Stencil Benchmarks                             | 94  |

|    |       | 5.4.2 Case Study: Haar Face Detection                           | 99  |

|    | 5.5   | Related Work                                                    | .01 |

| 6  | Con   | clusion 1                                                       | 104 |

|    | 6.1   | Dissertation Summary and Contributions                          | 05  |

|    | 6.2   | Future Directions                                               | .06 |

| Bi | bliog | raphy 1                                                         | 12  |

# LIST OF TABLES

| 1.1 | Summary of techniques presented in this dissertation              | 6   |

|-----|-------------------------------------------------------------------|-----|

| 3.1 | Benchmarks for RTL power estimation                               | 46  |

| 3.2 | Training time of different ML models                              | 47  |

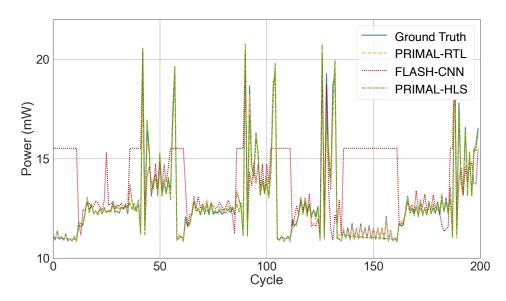

| 3.3 | Accuracy and speedup of PRIMAL-RTL, FLASH-CNN, and                |     |

|     | PRIMAL-HLS against gate-level power analysis on test sets         | 51  |

| 4.1 | Performance and area comparison of different arbitration policies | 69  |

| 5.1 | Timing and resource usage comparison with baseline where the      |     |

|     | minimum number of memory banks is used                            | 95  |

| 5.2 | Timing and resource usage comparison with baseline, where the     |     |

|     | number of memory banks is restricted to be a power-of-two         | 96  |

| 5.3 | Execution time of TraceBanking on Motion_LV with different in-    |     |

|     | put array sizes                                                   | 97  |

| 5.4 | Execution time of TraceBanking with reduced memory trace          | 98  |

| 5.5 | Timing and resource usage comparison of two face detection de-    |     |

|     | signs                                                             | 100 |

# LIST OF FIGURES

| 1.1<br>1.2                                           | Digital design flow with HLS                                                                                                                                                                                                                                                                                              | 2                                            |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1.3                                                  | different abstraction levels                                                                                                                                                                                                                                                                                              | 4<br>7                                       |

| 2.1<br>2.2<br>2.3<br>2.4                             | Digital design flow with HLS                                                                                                                                                                                                                                                                                              | 14<br>22<br>24<br>28                         |

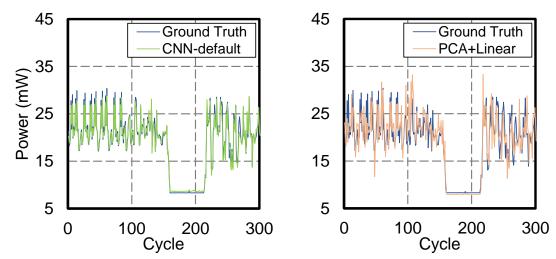

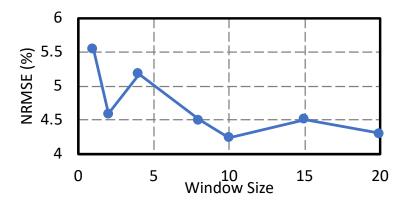

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5                      | Conventional ASIC power estimation flow vs. PRIMAL<br>Two phases of the PRIMAL workflow                                                                                                                                                                                                                                   | 32<br>35<br>38<br>39                         |

| 3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11             | tion methods<br>Default 1D and 2D feature encoding<br>Graph-based register-to-pixel mapping methods<br>Performance of different machine learning models on test sets<br>Ground truth vs. CNN-default and PCA+Linear for RISC-V<br>3D rendering trace comparison<br>SystemC power estimation accuracy of NoCRouter using a | 40<br>41<br>43<br>47<br>48<br>53             |

| 4.1<br>4.2<br>4.3<br>4.4                             | VGG16 CNN modelProposed flow of distilling logic from tracesProposed flow of distilling logic from tracesArchitecture diagram for router arbitrationArchitecture diagram for router arbitrationConvert tree models to combinational logicConvert tree models to combinational logicComparisons with dif-                  | 57<br>59<br>63<br>66                         |

| 4.5<br>4.6<br>4.7                                    | ferent policies                                                                                                                                                                                                                                                                                                           | 67<br>71<br>72<br>73                         |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8 | Hardware template for memory banking                                                                                                                                                                                                                                                                                      | 82<br>83<br>85<br>87<br>88<br>90<br>93<br>99 |

# CHAPTER 1 INTRODUCTION

With the end of Dennard scaling, the performance improvement of singlecore microprocessors has significantly slowed down in the past decade [51]. In order to satisfy the stringent performance and power requirements under current and future application scenarios, modern computational platforms are increasingly relying on parallel and/or heterogeneous processing to achieve high performance under a tight power budget. Multi-core CPUs are now prevalent in embedded systems [13], desktop- and server-grade computers [72, 74], as well as supercomputers [70]. Hardware acceleration using specialized accelerators is also becoming popular in both cloud and embedded computing platforms. In fact, FPGA and ASIC accelerators are now empowering a number of major products and services provided by some of the industry giants in their datacenters [11, 36, 81], while also being integrated into smartphones [55] and self-driving cars [113].

Unfortunately, high performance and power efficiency often come at the cost of the scale and complexity of modern hardware platforms. Notably, the latest Apple M1 system-on-chip (SoC) contains sixteen billion transistors, with an eight-core CPU, an eight-core GPU, and a neural engine for machine learning (ML) workloads [13]. The NVIDIA GPUs are massively parallel with thousands of CUDA cores and contain specialized accelerators for ray tracing and tensor computation [114, 115]. Hardened AI engines are also introduced into modern FPGAs which have already incorporated dedicated DSP units and memory modules [165]. Furthermore, the hardware industry is rapidly redesigning and updating their products to adapt to the emerging applications. The increase

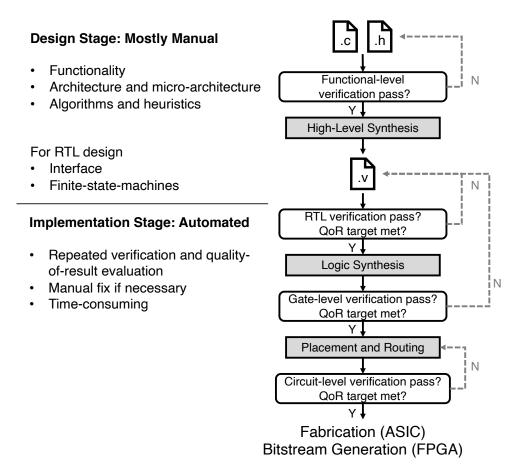

Figure 1.1: Digital design flow with HLS — The design stage is still mostly manual even with the assistance of HLS. The implementation stage, including synthesis, placement, and routing, is mostly automated by EDA tools. Hardware designs must be iteratively modified to pass verification and meet QoR targets.

in complexity and the urge for fast development are posing significant chal-

lenges to both hardware designers and the existing electronic design automa-

tion (EDA) tools.

### 1.1 Challenges in Digital Design: Productivity and Quality

Figure 1.1 shows a typical hardware design flow based on high-level synthesis (HLS)<sup>1</sup>. While the implementation of digital circuits is highly automated with the assistance of EDA tools, the hardware is usually designed manually by experienced engineers. At the design stage, developers must first provide a functional description of the hardware. In cases where the more traditional register-transfer-level (RTL) design methodology is applied, developers then further specify the RTL description including the connection of sub-modules, interfaces, and the logic and state transition of each sub-module. HLS raises the level of abstraction from RTL to the behavioral level and automates the generation of hardware microarchitecture. However, the design of hardware architecture is still not fully automated. Furthermore, modern hardware relies on carefully-designed heuristics to make decisions at run time, and the design of these heuristics is mostly manual.

Hardware designers rely on their intuition and experience to search for good design points in the vast design space. For modern hardware platforms, this process is becoming more and more challenging because of the even larger design space and the potentially different design trade-offs brought by new applications. Under this scenario, experience from past projects may not lead to successful design decisions, and the heuristics that were effective may no longer be satisfying for the new hardware. As a result, developers have to spend many more iterations to reach a good design point, and for every iteration the EDA tools must be rerun for functional verification and QoR evaluation. In some cases, it might be out of the designers' capability to design an effective heuristic

<sup>&</sup>lt;sup>1</sup>More traditional hardware design flows start from the RTL design step.

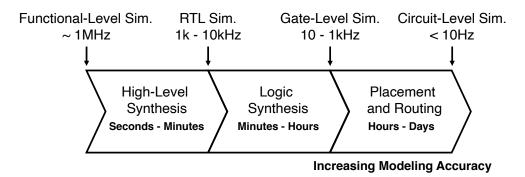

Figure 1.2: Time consumption of EDA steps and simulation throughput at different abstraction levels — Modeling accuracy increases at lower levels of abstraction. The speed of cycle-level simulation supported by SystemC [1] or GEM5 [99] is between functional-level simulation and RTL simulation.

algorithm or find a satisfying design point in a limited amount of time, and the final hardware implementation will be sub-optimal. The growing complexity of hardware systems will make manual hardware design more challenging and time-consuming.

Even without the increased number of design iterations, optimizing and implementing a hardware design is a time-consuming process. Figure 1.2 shows a rough breakdown of the time required at each step of the digital design flow. For large designs, the implementation stage itself may take hours or days, and the simulation at lower levels of abstraction can be as slow as ten cycles per second. Despite the low speed/throughput of these steps, they are necessary for designers to obtain meaningful evaluation results in the current hardware design flow, because modeling at earlier steps or higher levels of abstraction is not accurate enough. Combined with the increased number of design iterations, the turn-around time of hardware design will quickly become intolerable for fast-paced development.

# 1.2 Trace-Based Design-Specific Learning for Agile Hardware Design

There is an emerging trend of applying ML to EDA [69]. Existing works have explored a variety of topics including high-level modeling [44, 150, 175], design-space exploration [97, 109, 149, 158], automated architectural and micro-architectural design [30, 60, 133, 146, 171, 182], verification [68, 78], placement [107, 143, 164, 173], and layout pattern generation [170, 177]. These techniques have been shown to achieve superior performance on a variety of tasks in the EDA toolchain, and are able to significantly accelerate the hardware design flow by providing assistance to developers.

While ML techniques are shown to be effective for EDA problems in existing work, learning a design-agnostic model that performs well for any arbitrary design is very difficult. A design-agnostic ML model must learn the underlying characteristics of the target technology library and the optimization algorithms in the EDA tool flow. Due to the complexity of the digital design flow, many algorithms used in EDA are highly sophisticated and stochastic. Modern ML models would require a massive amount of training data from many different designs to effectively learn the behavior of these algorithms. In addition, hardware designs from different application domains have distinct characteristics. Without a collection of comprehensive datasets, new designs are likely to be out of the training distribution, causing the ML models to make inaccurate predictions.

Unfortunately, due to the lack of open-source designs and the long execution time of EDA tools, collecting and constructing large and useful datasets for

| Technique          | PRIMAL                     | Circuit Distillation             | TraceBanking             |

|--------------------|----------------------------|----------------------------------|--------------------------|

| Traces Used        | Gate-level/RTL/Cycle-level | Cycle-level                      | Functional-level         |

| Learning Technique | ML                         | ML & RL                          | Graph-based data mining  |

| Target Designs     | Hardened IP cores          | Partially-reconfigurable modules | Specialized accelerators |

| Design Metric      | Power                      | Performance & Area               | Performance              |

Table 1.1: Summary of techniques presented in this dissertation.

EDA problems remains a daunting task. An alternative is to use ML for designspecific learning. In this setting, the data collection effort is greatly reduced since the training data can be easily acquired from the given design. Furthermore, with design-specific learning, ML models only need to learn about the target design. The behavior of hardware designs is usually deterministic. In addition, while the ML models still need to learn the behavior of the EDA tools on the target design, this learning task is much easier than learning complete EDA algorithms. As a result, design-specific models can usually provide more detailed and more accurate predictions than their design-agnostic counterparts. In this dissertation we focus on using design-specific learning to improve the quality of one single design.

We argue that simulation traces generated by various stages of the hardware design flow are a good source of information for design-specific learning. Hardware developers often run millions or even billions of cycles of tests to guarantee the correctness of their designs and discover performance bottlenecks. Furthermore, depending on the level of abstraction, simulation traces contain different levels of details about the design: (1) Functional-level simulation verifies the functional correctness of a software-specified design and provides a sequence of transactions that is useful for understanding the high-level functional behavior of the design; (2) Cycle-level simulation evaluates the latency and throughput of the design while exposing the value of critical signals in each cycle for analysis and verification; (3) Simulation at RTL or lower ab-

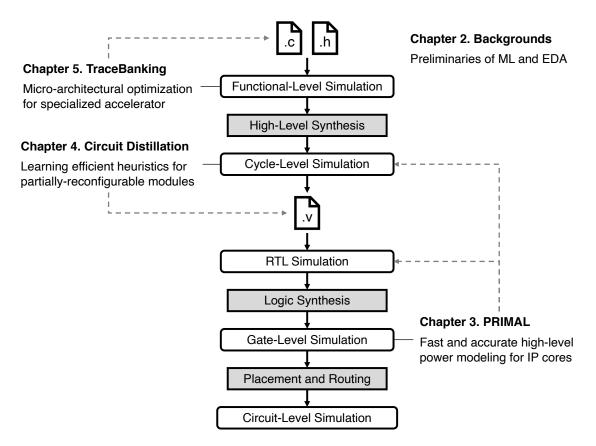

Figure 1.3: Dissertation outline.

straction levels exposes more internal details of the design, better reflects its timing behavior, and can be used to calculate the power and thermal characteristics of the underlying circuit. These details are necessary for accurate and fine-grained analysis of hardware designs. By collecting and analyzing these details, trace-based learning with ML can effectively assist the hardware design process.

### 1.3 Dissertation Overview

In this dissertation we introduce three trace-based, design-specific learning techniques for agile hardware design and design automation. As shown in

Figure 1.3, our research aims to improve both the optimization and modeling aspects of the hardware design flow. Moreover, our proposed techniques address the challenges that arise from optimizing different hardware design metrics, including performance, area, and power. Table 1.1 shows the coverage of this dissertation, which spans multiple levels of hardware design abstraction and explores a rich set of learning techniques. A more detailed overview of this dissertation is as follows:

- Because of the broad coverage of this dissertation, Chapter 2 is dedicated to introducing the necessary background for readers to get a better understanding of the techniques discussed in this dissertation. We will introduce the digital design flow and also broadly discuss several widely-used ML techniques, including linear and tree-based ML models, deep learning (DL), and reinforcement learning (RL).

- Chapter 3 presents PRIMAL, a ML-based methodology that provides finegrained RTL and cycle-level power estimation for IP cores. In this work we explore the potential of using DL models to characterize large circuit modules such as RISC-V processor cores and accelerators designed using HLS. Our experiments show that for RTL power estimation, convolutional neural networks can effectively model the power of large hardware modules, even if the test workloads are completely independent from the training sets. PRIMAL can achieve less than 5% error on cycle-by-cycle RTL power estimation while providing around 50× speedup compared with gate-level power analysis. This work was published in DAC'19 [186]. For cycle-level power estimation, we leverage recurrent neural networks to tolerate the inaccuracies in cycle-level simulation traces. Thanks to the faster simulation throughput at cycle level, we were able to achieve an-

other 3.5× speedup over our RTL power estimation technique on a collection of HLS accelerators, with marginal degradation in estimation accuracy.

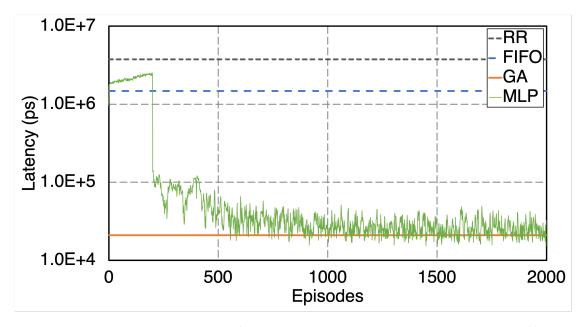

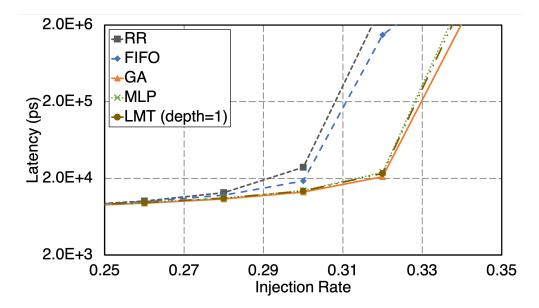

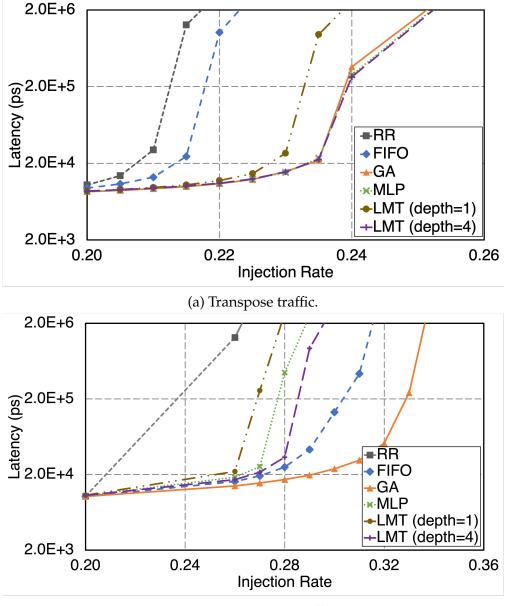

- Chapter 4 proposes a fully automated methodology to directly learn combinational logic from simulation traces and presents a case study on a network-on-chip (NoC) router arbitration task. Specifically, we leverage deep RL to learn a neural network (NN) agent which implements an optimized arbitration policy from simulation. The proposed Circuit Distillation flow then uses tree-based ML models as a bridge between the learned NN policy and a compact, combinational logic implementation. Experiments show that the learned arbitration logic is able to achieve a 64× reduction in average packet latency and a 5% improvement in network throughput over the baseline FIFO policy under the training traffic. This work has been accepted to DAC'2021.

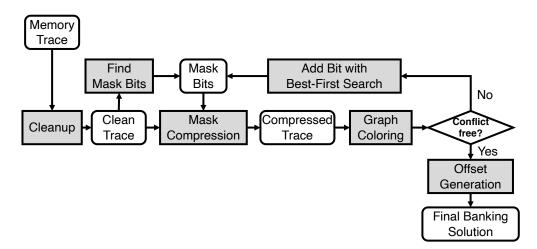

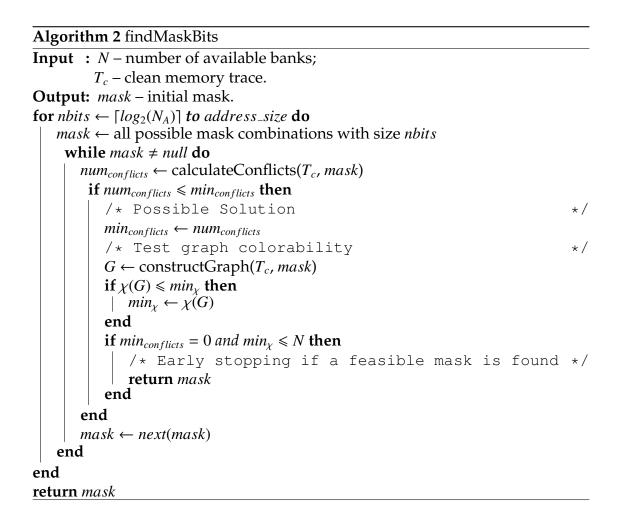

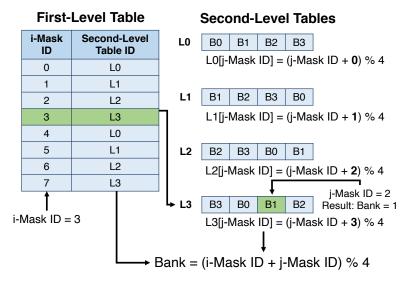

- Chapter 5 presents TraceBanking, a data-driven approach to automatically generating on-chip memory banking solutions for softwareprogrammable FPGAs. Our approach takes a memory trace of the target application as input and uses a graph-coloring-based algorithm to generate an efficient memory banking with no conflicts. Compared with existing compile-time memory partition techniques, our approach can handle arbitrary memory access patterns that are fixed at run time. This work was published in FPGA'17 [184].

- Chapter 6 summarizes the contributions of this dissertation and discusses future research directions.

### **1.4** Collaborations, Funding, and Previous Publications

This dissertation would not be possible without the contributions of my colleagues within the Zhang Research Group and Batten Research Group in the Computer Systems Laboratory at Cornell University, as well as collaborators from University of California Los Angeles (UCLA), Lehigh University, and the VLSI research group at NVIDIA. My advisor and committee chair, Prof. Zhiru Zhang, provided valuable suggestions and assistance to all the projects mentioned in this dissertation. The ideas of the high-level power modeling techniques presented in Chapter 3 originated from a discussion with Dr. Mark Ren, Dr. Yanqing Zhang, Dr. Ben Keller, and Dr. Brucek Khailany at NVIDIA research during my summer internship in 2018, and we collaborated on the RTL power estimation part of the PRIMAL project. The HLS power estimation part of PRIMAL is a collaboration with Dr. Young-kyu Choi and Prof. Jason Cong at UCLA. Dr. Choi and Prof. Cong provided valuable support on cycle-level simulation of HLS designs. The Circuit Distillation project in Chapter 4 was done in collaboration with Prof. Jieming Yin at Lehigh University and Hanyu Wang from Shanghai Jiao Tong University<sup>2</sup>. The initial idea of tackling this problem arose from Prof. Yin's paper on learning NoC arbitration policy using reinforcement learning [171]. Prof. Yin also provided detailed suggestions on the usage of the GEM5 simulator [99], the hyperparameter settings during training, and the writing of the submission. Khalid Al-Hawaj from Prof. Christopher Batten's group contributed significantly to the TraceBanking project presented in Chapter 5.

This dissertation was supported in part by a DARPA Young Faculty Award,

<sup>&</sup>lt;sup>2</sup>Hanyu was a (remote) research intern at Cornell when participating in this project.

NSF Awards #1337240, #1453378, #1512937, #1909661, the Intel ISRA Program, the Semiconductor Research Corporation (SRC), and research gifts from Xilinx, Inc and NVIDIA Corporation. A complete list of my publications during my Ph.D. in reverse chronological order is as follows:

- Yuan Zhou, Hanyu Wang, Jieming Yin, and Zhiru Zhang, Distilling Arbitration Logic from Traces using Machine Learning: A Case Study on NoC, to appear in Design Automation Conference (DAC), December 2021.

- Eshan Singh, Florian Lonsing, Saranyu Chattopadhyay, Maxwell Strange, Peng Wei, Xiaofan Zhang, Yuan Zhou, Jason Cong, Deming Chen, Zhiru Zhang, Priyanka Raina, Clark Barrett, and Subhasish Mitra, A-QED Verification of Hardware Accelerators, Design Automation Conference (DAC), July 2020.

- 3. Weizhe Hua, Yuan Zhou, Christopher De Sa, Zhiru Zhang, and G. Edward Suh, **Channel Gating Neural Networks**, *Thirty-third Conference on Neural Information Processing Systems (NeurIPS)*, December 2019.

- 4. Weizhe Hua, Yuan Zhou, Christopher De Sa, Zhiru Zhang, and G. Edward Suh, **Boosting the Performance of CNN Accelerators with Dynamic Fine-Grained Channel Gating**, *International Symposium on Microarchitecture (MICRO)*, October 2019.

- Yuan Zhou, Haoxing Ren, Yanqing Zhang, Ben Keller, Brucek Khailany, and Zhiru Zhang, PRIMAL: Power Inference using Machine Learning, *Design Automation Conference (DAC)*, June 2019.

- Yi-Hsiang Lai, Yuze Chi, Yuwei Hu, Jie Wang, Cody Hao Yu, Yuan Zhou, Jason Cong, and Zhiru Zhang, HeteroCL: A Multi-Paradigm Programming Infrastructure for Software-Defined Reconfigurable Computing,

International Symposium on Field-Programmable Gate Arrays (FPGA), February 2019.

- 7. Steve Dai, Yuan Zhou, Hang Zhang, Ecenur Ustun, Evangeline F.Y. Young, and Zhiru Zhang, Fast and Accurate Estimation of Quality of Results in High-Level Synthesis with Machine Learning, International Symposium on Field-Programmable Custom Computing Machines (FCCM), April/-May 2018.

- 8. Yuan Zhou, Udit Gupta, Steve Dai, Ritchie Zhao, Nitish Srivastava, Hanchen Jin, Joseph Featherston, Yi-Hsiang Lai, Gai Liu, Gustavo Velasquez, Wenping Wang, and Zhiru Zhang, Rosetta: A Realistic High-Level Synthesis Benchmark Suite for Software Programmable FPGAs, International Symposium on Field-Programmable Gate Arrays (FPGA), February 2018.

- Yuan Zhou, Khalid Al-Hawaj, and Zhiru Zhang, A New Approach to Automatic Memory Banking using Trace-Based Address Mining, International Symposium on Field-Programmable Gate Arrays (FPGA), February 2017.

### CHAPTER 2

#### PRELIMINARIES ON EDA AND MACHINE LEARNING

In this chapter we provide background knowledge for the techniques presented in this dissertation. The rest of this chapter will introduce the electronic design automation (EDA) flow, basic concepts and important techniques of machine learning (ML), as well as the application of learning-based methods in EDA and computer architecture.

### 2.1 Overview of the EDA Flow

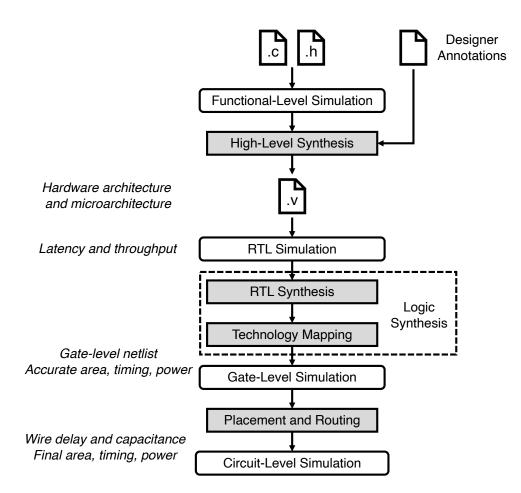

Figure 2.1 shows the digital design flow with more details. As mentioned in Chapter 1, designing a digital circuit is a time-consuming process that involves many design iterations. The process of finding a satisfactory design point is usually referred to as design space exploration (DSE). Each promising design point must be repeatedly verified and evaluated at different levels of abstraction, and manual optimizations are necessary if the design fails to meet the constraints. When evaluating the design, some metrics such as area and frequency can be directly provided by the EDA tools, while other metrics like latency and power can only be obtained by running simulation using a comprehensive set of workloads. The extensive use of simulation further increases the design time because detailed simulation is very time-consuming, especially at lower levels of abstraction such as gate-level and circuit-level.

As shown in Figure 2.1, accurate estimations of the quality-of-result (QoR) metrics can only be obtained at later stages of a typical EDA flow. To facilitate DSE, ideally designers would like such estimations to be available earlier in

Figure 2.1: Digital design flow with HLS — Accurate estimations of many QoR metrics are only available at lower levels of abstraction because each step in the design flow introduces additional details about the design.

the design flow, where the level of abstraction is higher and exploring different design points is easier. Unfortunately, high-level modeling of digital circuits is inherently challenging, because each step in the EDA flow introduces many additional details about the design which are hard to predict at higher levels of abstraction. Chapter 3 focuses on the power estimation aspect of this problem. The rest of this section briefly introduces each step in the EDA flow.

**High-Level Synthesis** The high-level synthesis (HLS) step converts a behavioral-level description of the design to an register-transfer-level (RTL) de-

scription. The behavioral-level description can be specified in C/C++ [71, 168], OpenCL [73, 167], or Python [88, 166]. With HLS, the designer no longer has to design the interface between hardware modules or the finite-state-machine (FSM) of each module. Modern HLS tools usually provide a set of predefined interface protocols. In addition, the scheduling and binding algorithms in the HLS tools are able to directly generate optimized datapath and FSM from the behavioral-level description. The designers are given the flexibility to specify additional optimizations to the generated hardware, such as parallelizing the computation, customizing the datatype, or partitioning the data memory for higher memory bandwidth. While the decisions of where and how to add these optimizations need to be made manually in modern HLS tools, automatically finding good combinations of the optimizations and effective optimization solutions are active lines of research.

The RTL source code generated by the HLS tools accurately describe the architecture and microarchitecture of the hardware. The reports from HLS tools contain a lot of useful information such as the type and count of operators, the size of memories, and the latency of fixed-latency hardware modules. For hardware blocks with variable latency, accurate performance measurements can be obtained from RTL simulation. However, the low-level implementation details of the design are yet to be determined by the downstream flow. Even with the information from the generated RTL representation, the HLS tools have limited knowledge on the selection of operators or the sizing of gates, and can only provide very crude estimates of wire delay and capacitance. All these missing details make accurate modeling at RTL and higher abstraction levels extremely challenging. **Logic Synthesis** Logic synthesis refers to the step which transforms the RTL description written in hardware description languages (HDLs) into a technology-specific gate-level netlist. As shown in Figure 2.1, logic synthesis can be further divided into two steps: RTL synthesis and technology mapping. RTL synthesis converts the HDL into a technology-independent logic representation. This process involves several key steps, including RTL elaboration, datapath synthesis, and logic minimization. RTL elaboration converts the HDL code into an abstract, intermediate format which is suitable for downstream processing of the synthesis tool. The common operators such as addition and multiplication are directly converted to logic by datapath synthesis, while the rest of the design are synthesized to logic and further optimized by the logic minimization step.

Technology mapping takes the optimized technology-independent logic representation as input and maps it to components provided by the technology library. For ASICs, the technology library contains basic elements of digital circuits, such as flip-flops and combinational logic gates with different drive strengths, memory modules, and register files. When mapping to FPGAs, the mapper is limited to a small set of elements provided by the FPGA architecture, including look-up tables (LUTs), flip-flops, digital-signal-processing (DSP) units, and block RAMs (BRAMs).

After technology mapping, the gate-level implementation of the design is precisely defined. The synthesis tool now has complete information about the size, capacitance and delay of each gate in the design. As a result, the tool will be able to provide more accurate estimations of area, frequency, and power, which are often used as indicators of the design quality in practice. However, the gatelevel netlist still does not contain any topological information, so the details of the wires and interconnects are unavailable. The wire delay and capacitance significantly affect the frequency and power consumption of the design. Without these details, the modeling accuracy at gate-level is still limited.

**Placement and Routing** The placement and routing steps are often referred to as physical design. For ASIC design, these steps arrange the components of the gate-level netlist on the chip area and connect them together without violating the constraints specified by the fabrication technology. As the names suggest, the placement step places the standard cells and macros onto the chip area, and the routing step connects the components together using metal wires. For FP-GAs, the positions of the logic elements are fixed for each device. Therefore, rather than performing placement and routing on an empty chip area, the placer for FPGAs allocate the elements in the synthesized netlist onto the predefined positions, while the routing algorithm for FPGAs configures the programmable interconnects on the FPGA to connect the logic elements. Since the solution spaces of the placement and routing problems are large and hard-to-predict, stochastic algorithms are often used to search for good solutions within a limited amount of time. In modern EDA toolchains, the placer and router often work together to generate higher-quality layouts: the placer tries to predict the final routing quality and generate easy-to-route placements, while the router may slightly modify the placement to improve the routing quality. Because of the complexity and randomness of these steps, it is challenging to accurately estimate all the circuit-level details even from gate-level.

### 2.2 Machine Learning Overview

In the past decade, ML techniques have been applied to a wide variety of fields including autonomous driving [56], gaming AI [134, 135], image classification and captioning [62, 172], machine translation [142, 151], protein structure prediction [131], and trading [14, 176]. Most of these successes leverage deep learning (DL), a branch of ML that uses deep neural networks (DNNs) with a large amount of parameters to approximate arbitrary target functions. Instead of presenting a rigorous, mathematical introduction to ML, the purpose of this section is to help the readers build an intuitive understanding of the basic concepts and important techniques in the field of ML. For a more comprehensive introduction, interested readers can refer to the abundant online resources [4, 5, 6, 117] or textbooks [54, 111].

At a high level, ML techniques learn from data and try to model the probability distribution of data. The process of "learning from data" is referred to as **training**, and the process of evaluating the learned model using another portion of available data is called **testing** or **evaluation**. During training, a training dataset is provided to the ML model, and the training algorithm tries to optimize a carefully-designed objective function. Since the model only has access to a sampled subset of the input space, it will never observe the complete data distribution, and the distribution in the training set often slightly differs from the actual data distribution because of the randomness of sampling or the bias in the data collection process. As a result, the ML model will **overfit** the training set if it only focuses on perfectly fitting the training distribution but overlooks the generalization to the whole input space. This often happens when the model is too complicated for the task. On the contrary, if the model does not have enough complexity to fit the training distribution to a satisfying degree, we say the model is **underfitting**. To balance the complexity and generalizability of the model, the objective function during training often has the form shown in Equation 2.1:

$$J(\mathbf{w}, \mathcal{D}) = L(\mathbf{w}, \mathcal{D}) + \lambda R(\mathbf{w})$$

(2.1)

where **w** refers to the learnable parameters of the model and  $\mathcal{D}$  refers to the training set. The first term on the right hand side,  $L(\mathbf{w}, \mathcal{D})$ , is called the **loss** term and represents how well the model performs on the training set. The second term,  $\lambda R(\mathbf{w})$ , is a **regularization** term to constrain the model's complexity and avoid overfitting, where  $\lambda$  and  $R(\mathbf{w})$  are often called the regularization factor and the regularization function, respectively. Notice that the form in Equation 2.1 is consistent with constrained optimization problems, and the goal of ML techniques is just to optimize an objective function. As a result, by a broad definition, traditional optimization techniques such as combinatorial optimization methods can also be considered as a form of ML.

Depending on the specific use case, ML techniques can be roughly categorized as **supervised learning**, **unsupervised learning**, and **reinforcement learning**. In supervised learning, the ML models learn from labeled training data. Specifically, each training data sample is associated with a categorical label for classification tasks, or a numerical label for regression tasks. As a result, supervised learning techniques actually model the probability distribution of labels given the input. In contrast, unsupervised learning techniques learn from unlabeled data and try to directly model the distribution of the input data. For reinforcement learning, no training dataset is directly provided to the machine learning model. Instead, the model (also called an "agent" in the reinforcement learning setting) is given an environment that can respond to the decisions made by the model, as well as a user-defined reward function which evaluates the model's performance based on the state transition in the environment. Under this setup, the goal is to train an agent which can make optimal decisions according to information provided by the environment. During training, the agent repeatedly makes decisions, and new training data is generated on-the-fly every time the agent makes a new decision.

The rest of this section will briefly discuss both supervised learning and reinforcement learning techniques that are used in the approaches introduced in this dissertation. Section 2.2.1 outlines linear models and tree-based models. Section 2.2.2 introduces the fundamentals of deep learning. We also discuss the basics of reinforcement learning in Section 2.2.3, with a focus on deep reinforcement learning.

### 2.2.1 Linear and Tree-Based Models

Linear models and tree-based models are widely-used, traditional ML models. In contrast to deep learning models that can approximate arbitrary target functions, these two types of models only target a specific type of functions. While this constraint limits the expressiveness of these models, it also allows them to be extremely efficient when the function to be approximated falls into the category that can be accurately modeled by them. Without special mentioning, the following discussions on linear and tree-based models assume a single-target regression scenario. **Linear Models** As one of the simplest ML models, linear models assume the target function has a linear relationship with the input features. In a single-target regression setting, a linear model can be represented in the form shown in Equation 2.2:

$$f(\mathbf{x}) = \sum_{i=1}^{M} w_i x_i + b \tag{2.2}$$

where **x** is an *M*-dimensional input feature vector of real numbers { $x_1, ..., x_M$ }, **w** = { $w_1, ..., w_N$ } represents the learnable linear coefficients, and *b* is a learnable bias value. Suppose the training set is represented as  $\mathcal{D} = \{(\mathbf{x}^1, y^1), ..., (\mathbf{x}^N, y^N)\}$ , for regression tasks common objective functions to optimize during training are shown in Equation 2.3 [65, 147].

$$J(\mathbf{w}, \mathcal{D}) = \frac{1}{N} \sum_{i=1}^{N} (f(\mathbf{x}^{i}) - y^{i})^{2}$$

Ordinary Least Squares

$$\frac{1}{N} \sum_{i=1}^{N} (f(\mathbf{x}^{i}) - y^{i})^{2} + \lambda ||\mathbf{w}||_{1}$$

Lasso Regression (2.3)

$$\frac{1}{N} \sum_{i=1}^{N} (f(\mathbf{x}^{i}) - y^{i})^{2} + \lambda ||\mathbf{w}||_{2}$$

Ridge Regression

If trained with different loss functions, linear models are also very effective on classification tasks when samples from different classes are linearlyseparable. For binary classification tasks, linear models can be used to predict class labels by testing  $f(\mathbf{x}^i) > 0$  or by estimating the probability of the data sample belonging to class one with a logistic function ( $p(y^i = 1|\mathbf{x}^i) = \frac{1}{1+e^{-f(\mathbf{x}^i)}}$ ). The latter approach is often referred to as logistic regression [66]. Linear support vector machines (SVMs) improve the robustness of linear classifiers by enforc-

Figure 2.2: Examples of tree-based models for regression tasks.

ing a minimum margin between any training data sample and the learned decision boundary [41].

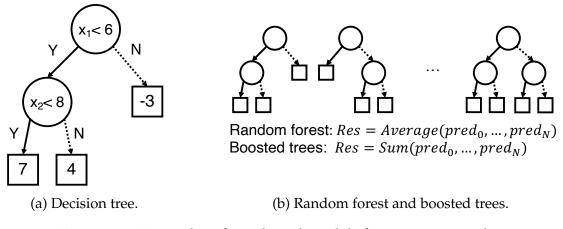

**Tree-Based Models** Tree-based models approximate the target function by repeatedly partitioning the input space and learning a separate function in each partition. As the simplest form of tree-based models, a decision tree recursively partitions the input space using axis-parallel splits and learns a constant value in each partition. Figure 2.2a shows a decision tree for regression. The leaf nodes encode the final predicted values, which are constants for decision trees. Multiple decision trees can be assembled together using bagging or boosting, resulting in random forests [63] or boosted trees [31] as shown in Figure 2.2b. When more complicated models are used at the leaf nodes, such trees are referred to as model trees. For example, if linear regression models are used at the leaves, the resulting linear model tree will be able to learn piecewise-linear functions.

During training, a decision tree or model tree is gradually "grown" by repeatedly partitioning the training data. At the root node, all the training data is analyzed and a certain gain function is computed to find the best split that maximizes the gain. For classification problems, the difference of gini impurity or mutual information are common gain functions, while for regression problems the mean-squared error between the predictions and ground-truth labels can be used [23]. After the training data is split into two partitions, the same process is repeated at the children of the root node, where each child node only considers one partition of the data. This procedure is applied recursively until the splitting condition is not met. In this case, the node where the partitioning process terminates is a leaf node, and a function is used to fit all training data that arrives at this node.

A decision tree or model tree without any regularization is very prone to overfitting, because it can keep partitioning the input space until there are only a few samples at each leaf. Such a tree is unlikely to generalize well to unseen inputs. Common regularization methods for tree models include constraining the maximum depth, the minimum samples at each leaf, the minimum number of samples to make a split, and the minimum gain to make a split. Bagging is also an effective method to avoid overfitting for tree-based models.

## 2.2.2 Deep Learning

The fundamental building blocks of deep learning (DL) models are linear "layers" followed by non-linear activation functions. While a single layer has limited expressiveness, the flexibility of combining multiple layers in various ways enables DL models to accurately approximate a wide range of target functions. The non-linear activation functions are crucial for DL models to represent com-

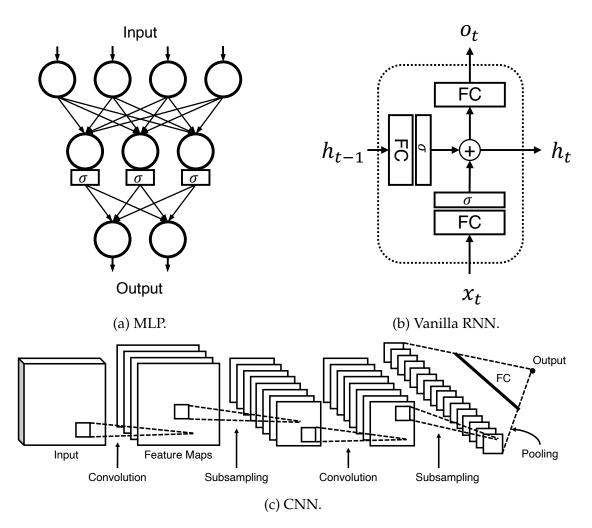

Figure 2.3: Examples of the most basic versions of different DL models — **MLP**: Only contains FC layers and activation functions. **Vanilla RNN**: The output  $o_t$  at each time step depends on the input at the current time step  $x_t$  and the hidden signal from the previous time step  $h_{t-1}$ . **CNN**: Performs repeated convolution and subsampling to the input image, where subsampling can be performed using either pooling layers or convolution layers with non-unit stride. One or more FC layers are used at the end of the network to generate outputs for regression or classification.

plicated nonlinear functions. Depending on the specific use case, common activation functions include sigmoid, hyperbolic tangent (tanh), and rectified linear unit (ReLU) [112] and its extensions [38, 61, 102].

Figure 2.3 shows the most basic versions of the DL models used in this

dissertation: multi-layer perceptrons (MLPs), convolutional neural networks (CNNs), and recurrent neural networks (RNNs). As the simplest type of DL model, MLPs only contain fully-connected (FC) linear layers and activation functions. RNNs are designed for sequence processing where the output at the current time step may depend on inputs from previous time steps. As shown in Figure 2.3b, the outputs from the previous time step are used to compute outputs at the current time step. While this recurrent connection enables RNNs to leverage information from the past, it also limits the parallelizability of the RNN models. Popular RNN models such as long short-term memories (LSTMs) [64] and gated recurrent units (GRUs) [34] have more sophisticated mechanisms to control the importance of historical information. CNNs specialize for image processing by replacing the fully-connected layers with convolution layers, which can be considered as large fully-connected layers with most elements being zeros. The convolution layers exploit local information from image patches, while global information is gradually collected through subsampling using pooling layers or convolution layers with non-unit stride. Figure 2.3c shows a basic CNN architecture for regression. Modern CNN models often feature small convolution filters [136], residual connections [62], and batch-normalization [75]. Computationally efficient CNN architectures use group convolution [87, 163] or depthwise-separable convolution [35, 67] to replace normal convolution layers, and apply channel shuffling [100, 178] to avoid significant accuracy degradation.

**Training** State-of-the-art DL models often contain many layers and millions of parameters in the weight matrices, enabling them to approximate extremely complicated functions. As a result, a large amount of training data is required

to properly optimize all parameters in the model without overfitting. For example, the smaller datasets for image classification contain tens of thousands of images [86, 91], the popular ImageNet dataset has several million images [130], while industrial datasets may contain tens of millions of training samples. It is impractical to directly optimize all parameters in the models with so many training samples using traditional solvers.

DL models are usually trained using stochastic gradient descent (SGD), where the whole training set is divided into small batches containing only tens to hundreds of training samples. For each batch, the model being trained first makes its predictions using its current version of parameters, and the loss function (the L term in Equation 2.1) on this batch is computed. If regularization is applied and the regularization function can be explicitly expressed as a regularization term (the R term in Equation 2.1), the regularization function is also computed based on the current version of parameters. The goal of training is to minimize the objective function (J in Equation 2.1), and the gradient of each parameter in the model can be computed from the objective function using the chain rule. For vanilla SGD, the parameters are then updated using the computed gradient values according to Equation 2.4:

$$\mathbf{w}_{n+1} = \mathbf{w}_n - \alpha \,\triangledown \,\mathbf{w} \tag{2.4}$$

where  $\mathbf{w}_n$  refers to the parameter values at batch *n*. The hyper-parameter  $\alpha$  is called the learning rate and is set by the user to control the step size of each update. To guarantee convergence, the learning rate is usually set to a small value and the model must be trained using a large number of batches. More advanced variants of SGD introduce additional mechanisms and hyper-parameters to es-

cape bad local minima [123, 141] and automatically adjust the learning rate for individual parameters [46, 83]. Training with SGD allows DL models to effectively exploit a large amount of training samples and be continuously updated with new data.

**Regularization** Due to the large capacity, DL models can easily overfit to training sets. The most basic regularization method for DL models is weight decay, which uses the L2 norm of all the weights as the regularization term<sup>1</sup>. Weight decay encourages the weights of the model to have small magnitudes so that a small change in the input would not cause drastic changes in the outputs. Dropout [137] randomly drops part of the output neurons in a layer with probability *p* by setting the output values of these neurons to zeros. Because a different set of neurons are present for each training batch, the neurons learn more robust representations by themselves instead of trying to correct other neurons' mistakes. During evaluation, no neuron is dropped and all the weights in the layer are multiplied by *p* to maintain the magnitude of the outputs. In practice, reducing the batch size during training also helps avoid overfitting. With smaller training batches, the sampling noise in each batch prevents the model from quickly converging to the optimal solution on the training set and results in a more generalizable model.

#### 2.2.3 Reinforcement Learning

Different from supervised learning and unsupervised learning where a training dataset must be provided in advance, reinforcement learning (RL) techniques

<sup>&</sup>lt;sup>1</sup>Similar to the regularization term of Ridge regression in Equation 2.3.

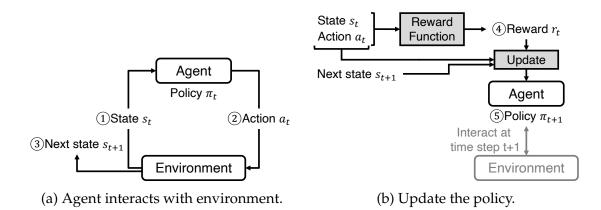

Figure 2.4: Overview of RL model training.

generate data during the training process and use this data to update a model that is used to make decisions. This model is often referred to as an "agent" in the RL setting. Figure 2.4 presents a high-level illustration of the RL training process. The goal of training is for the agent to learn an effective policy  $\pi$  which can make optimal decisions according to the information from the environment.

The agent is trained by repeatedly making decisions and interacting with the provided environment. At each time step t, the agent is provided with the state of the environment,  $s_t$ , and selects an action  $a_t$  according to its current policy  $\pi_t$ . The agent then interacts with the environment by performing action  $a_t$  and changes the environment's state from  $s_t$  to  $s_{t+1}$ . A reward value at the current time step,  $r_t$ , is computed based on  $s_t$ ,  $s_{t+1}$ , and  $a_t$  using a human-designed reward function. The internal parameters of the agent can then be updated using the tuple ( $s_t$ ,  $s_{t+1}$ ,  $a_t$ ,  $r_t$ ) from the current time step as well as tuples from earlier time steps. The updated policy,  $\pi_{t+1}$ , will be used in the next time step for selecting the most promising action.

Rather than taking a greedy approach and focusing on the immediate reward, the goal of the RL agent is to maximize the long-term cumulative reward. A common way of computing the long-term cumulative reward *R* from the current time step *T* to the future is shown in Equation 2.5, where a user-specified parameter  $\gamma$  determines whether to focus on near-term reward or long-term reward.

$$R = \sum_{t=T}^{\infty} \gamma^{t-T} r_t, 0 < \gamma < 1$$

(2.5)

**Q-Learning** One important branch of RL is Q-learning [160], where the agent directly tries to predict the long-term cumulative reward of each state-action pair (*s*, *a*). The predicted rewards, denoted as Q(s, a), are called Q-values, and the function that computes the Q-value of a given state-action pair is called the Q-function. When making a decision at time step *t*, the learned policy  $\pi_t$  simply chooses the action with the maximum Q-value. During training, the Q-values are updated following the famous Bellman equation:

$$Q^{\pi_{t+1}}(s_t, a_t) = r_t + \gamma \max_{a'}(Q^{\pi_t}(s_{t+1}, a'))$$

(2.6)

An intuitive explanation of Equation 2.6 is that the updated Q-value of the current state-action pair  $Q^{\pi_{t+1}}(s_t, a_t)$  equals to the reward at the current time step plus the maximum cumulative reward obtainable from the next state times a discount factor. Proof of convergence is out of the scope of our discussion, but in practice the Q-values usually converge well because of the exponential decay of long-term rewards.

**Deep Q-Learning** Traditional Q-learning techniques often use table-based approaches to store the Q-values. Table-based Q-learning is effective when the state space and action space are both small. When applied to computer architecture, the Q-value tables can be easily updated in hardware during execution [76, 110]. However, table-based Q-learning does not scale well to more complicated problems where the state space and action space are large. With the advance of DL, Mnih et al. propose deep Q-learning (DQN), which represents the Q-function using a DNN [108]. While losing the ability to be efficiently updated in hardware, DQN presents a unified and scalable approach to complicated, large-scale decision-making problems.

During training, the DQN agent is trained with SGD, and the loss function can be as simple as an L2 loss<sup>2</sup>. To encourage the agent to explore the environment, at the beginning of training, the agent has a high probability of choosing a random action instead of following the prediction of the neural network. This probability gradually decreases during the training process so that the agent can learn a stable policy towards the end of training. In addition, since the earlier decisions made by the agent affect the state of the environment, the training samples would be highly dependent on each other if the neural network is only trained using the latest state-action pairs. A "replay memory" mechanism is designed to alleviate the dependency problem and encourage the agent to sufficiently learn from its past experiences. The replay memory caches the stateaction pairs and rewards during training. At each time step, the training data to the neural network is randomly sampled from the replay memory.

${}^{2}L = (Q^{\pi_{t}}(s_{t}, a_{t}) - r_{t} - \gamma max_{a'}(Q^{\pi_{t}}(s_{t+1}, a'))^{2}$

#### CHAPTER 3

#### PRIMAL: POWER INFERENCE USING MACHINE LEARNING

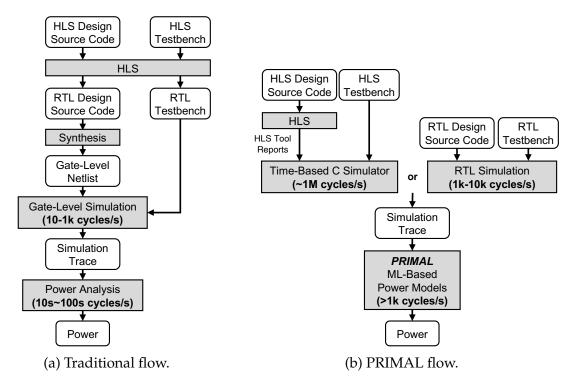

Modern VLSI design requires extensive optimization and exploration in a large design space to meet the ever stringent requirements with respect to performance, area, and power. Existing electronic design automation (EDA) tools can provide reasonably accurate area and performance estimates at registertransfer level (RTL) or even behavioral level with the aid of high-level synthesis (HLS) tools. However, in order to achieve power closure, designers must obtain detailed power profiles for a diverse range of workloads from different application use cases or even from different levels of design hierarchy. Currently, the common practice is to feed the gate-level netlist and simulation results to power analysis tools such as Synopsys PrimeTime PX (PTPX) to generate cycle-level power traces. Figure 3.1a depicts a typical ASIC power analysis flow, which offers accurate estimates but runs at a very low speed. The throughput of power analysis is in the order of 10-100s of cycles per second, while the gate-level simulation step for generating simulation traces runs at less than one thousand cycles per second. Given the high complexity of present-day ASIC designs, it can take hours or days to perform gate-level power analysis for one intellectual property (IP) core under desired workloads. Furthermore, power-directed optimization is an iterative process, which means designers have to repeat this time-consuming power estimation process after every optimization step. As a result, power analysis has become a critical bottleneck which prevents rapid design-space exploration.

An alternative is to analyze power above the gate level. There exists a rich body of research on power analysis at RTL or higher abstraction levels

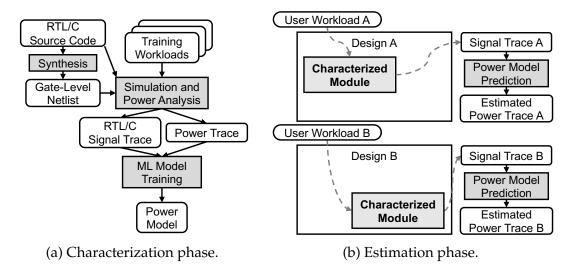

Figure 3.1: Conventional ASIC power estimation flow vs. PRIMAL — (a) With existing EDA tools, designers must rely on the time-consuming gate-level simulation and power analysis for accurate power profiles. (b) PRIMAL trains ML-based power models for reusable IPs. Using the trained models, detailed power traces are obtained by running ML model inference on RTL or timed C simulation traces.

[9, 12, 21, 29, 92, 126, 132, 140, 169]. These efforts typically make use of measured constants or simple curve fitting techniques such as linear regression to characterize the power of a given circuit, improving the speed of power analysis at the expense of estimation accuracy. For accurate power characterization, many low-level details of the circuit need to be modeled, including standard cell parameters, sizing of the gates, and clock gating status of the registers. Gate-level power analysis uses them to estimate the switching capacitance and activity factor of each circuit node. However, these low-level details are unavailable at (or above) RTL by design. It is also very difficult for simple analytical models or linear regression models to capture the complex nonlinear relationship between

the register toggles and the total switching capacitance.

In this chapter we introduce PRIMAL, a methodology based on machine learning (ML) for fast and accurate high-level power estimation. PRIMAL leverages gate-level power analysis to train ML models on a set of training workloads. These trained models can then be used to infer power profiles of the same IP core under a different set of user-specified workloads. Figure 3.1b illustrates the inference flow of PRIMAL, which only requires inputs from RTL simulation or C simulation with timing information to generate accurate power estimates at a much higher speed (>1k cycles per second). By greatly reducing the required number of gate-level simulation cycles, PRIMAL allows designers to perform power-directed design space exploration in a much more productive manner. The major technical contributions of this work are five-fold:

- 1. We present PRIMAL, a novel ML-based methodology for rapid power estimation with RTL or timed C simulation traces. The trained ML models can provide accurate, cycle-by-cycle power estimation for user workloads even when they differ significantly from those used for training.

- 2. We investigate several established ML models for RTL power estimation, and report trade-offs between accuracy, training effort, and inference speed. Our study suggests that nonlinear models, especially convolutional neural networks (CNNs), can effectively learn power-related design characteristics for large circuits.

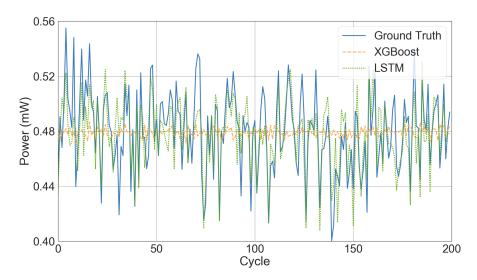

- 3. We propose to use long short-term memory (LSTM) [64] for HLS power estimation. Because LSTMs are designed for sequence processing, they are able to tolerate the inaccuracies in the simulation traces generated by C-based simulators by leveraging history information before the current

cycle.

- 4. For RTL power estimation, we demonstrate that PRIMAL is at least 50x faster on average than PTPX for cycle-accurate power estimation with a small error. Notably, our CNN-based approach is 35× faster than PTPX with a 5.2% error for estimating the power of a RISC-V core. PRIMAL also achieves a 15× speedup over a commercial RTL power analysis tool for average power estimation.

- For HLS power estimation, our LSTM-based approach offers an additional 3.5× speedup over the CNN-based RTL power estimation approach while achieving comparable estimation accuracy.

The RTL power estimation part of this chapter was published in DAC'19 [186]. The remainder of this chapter is organized as follows: Section 3.1 presents the overall methodology and intended use cases of PRIMAL. Section 3.2 introduces our feature construction methods. Experimental results for RTL and HLS power estimation are reported in Sections 3.3 and 3.4, respectively. Section 3.5 presents related works with additional discussions.

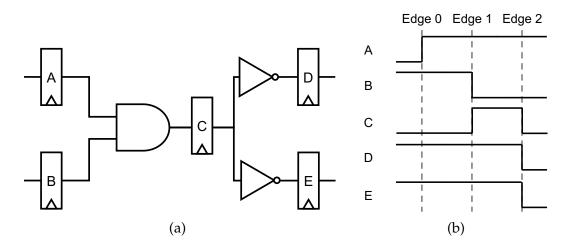

# 3.1 Methodology

Unlike previous works, PRIMAL uses state-of-the-art ML models for fast and accurate high-level power estimation. Figure 3.2 shows the two phases of the PRIMAL workflow<sup>1</sup>. The characterization phase (Figure 3.2a) requires an RTL/C model of the module, the gate-level netlist, and a set of training work-loads. RTL register or C variable traces are used as the input features, while

<sup>&</sup>lt;sup>1</sup>We assume C-based HLS design flows for HLS power estimation.

Figure 3.2: Two phases of the PRIMAL workflow — Power models are trained once per module. Models can then be used across different workloads, as well as in different designs that instantiate the module.

ground-truth power numbers for the training workloads are obtained from gate-level power analysis. The characterization process only needs to be performed once per IP block. The trained power models can then be used to estimate power for different user workloads in the estimation phase as illustrated in Figure 3.2b.

It is important to note that the training workloads may be very different from the actual user workloads. For example, designers can use functional verification tests to train the power models, which then generalize to realistic workloads. By using state-of-the-art ML models, our approach accommodates diverse workloads and can model large, complex circuit blocks. The ML models are trained for cycle-by-cycle power estimation, which provides a more detailed power profile than average power and enables more effective design optimization.

## 3.1.1 **RTL Power Estimation Methodology**

For RTL power estimation, the RTL register traces are used as input features during the characterization phase. More specifically, we use register switching activities in the simulation traces as input features. Compared with using all signals from the RTL simulation trace, only using register switching activities significantly reduces input feature size, prevents overfitting, and still captures the complete current state of the circuit. In addition, the mapping between RTL signals and gate-level registers can be retrieved from the logic synthesis tool report. Because we use cycle-accurate power traces from gate-level simulation as ground truth, the ML models are essentially learning the complex relation-ship between the switching power of all gate-level cells and register switching activities.

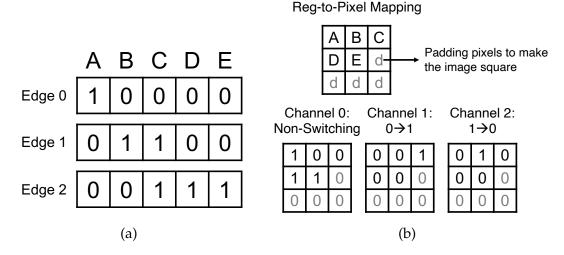

In this work we explore a set of established ML models for RTL power estimation. The classical ridge linear regression model is used as a baseline. We also experiment with gradient tree boosting, a promising non-linear regression technique [104]. For linear models and gradient tree boosting models, we apply principal component analysis (PCA) [80] to the input data to reduce model complexity and avoid overfitting. We also study the efficacy of deep learning (DL) models, which are capable of approximating more complex nonlinear functions. Specifically, we experiment with multi-layer perceptron (MLP) and CNN for RTL power estimation. MLP contains only fully-connected network layers and is more compute-efficient than CNN. However, the parameter count of MLP grows quickly with respect to the feature size of the design, resulting in overfitting and training convergence issues. CNNs have shown impressive performance in image classification tasks. Thanks to the structure of convolutional layers, the parameter count of CNNs does not increase significantly as input image size grows. As a result, CNN is a more scalable choice than MLP for large designs.

#### 3.1.2 HLS Power Estimation Methodology

For HLS power estimation, since we rely on timed software simulation at cycle level, the RTL register information is no longer available. As a result, we use C variable traces as the input features to the ML models. We leverage the FLASH simulator [33] to generate C/C++ source code annotated with timing information. Using the timing information from the HLS synthesis report, FLASH accurately estimates the execution time and simulates FIFO communication cycleaccurately. Because FLASH abstracts the binding and allocation information of the computational statements, it is several orders of magnitude faster than the RTL co-simulation provided by current HLS tools. The software simulation trace is obtained by compiling the annotated source code together with the testbench and running the generated executable.

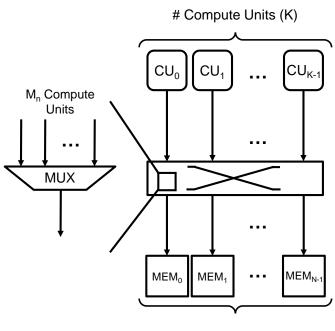

FLASH abstracts the binding and allocation information away to achieve speedup over RTL simulation. However, this abstraction also causes FLASH to simulate the computational statements in a cycle-approximate manner. In addition, the C variables do not have a one-to-one correspondence with RTL or gate-level signals, adding to the difficulty of accurately estimating power consumption. As a result, the values of the C variables in each cycle is only an incomplete and shifted approximation of the current state of the circuit, and may have poor correlation with the power of the circuit.